关键字:FPGA;SDRAM;Verilog;

1 引 言

在进行高速数据记录仪的开发中,由于硬盘固有的寻道延时,不能实现外部数据实时写入。采用固态硬盘成本又比较高,所以在设计中考虑外加大容量数据缓存。在各种随机存储器件中,SRAM的价格低,设计简单,但容量一般都不大;DDR速度快、容量大,但硬件和软件设计都比较复杂。SDRAM具价格低、体积小、速度快、容量大的优点,是满足高速数据记录设计带宽的理想器件。但是,与SRAM相比较,SDRAM的控制逻辑复杂,接口方式与普通的存储器差异很大。为了解决这个矛盾,需要设计专用的SDRAM控制器,本文中提出了SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。该设计采用了Altera公司的CycloneII系列EP2C35F484C8N作为主控芯片。系统工作时钟为75M。

2 SDRAM工作原理简介

本设计采用SDRAM芯片选用Winbond公司的W982516,4M×4BANKS×16BIT,两片并成32位数据总线,突发读写速度可达到300Mbytes/s。 W982516采用了54引脚的TSOP封装,工作电压为3.3V,并且采用同步接口方式(所有的信号都是时钟信号的上升沿触发),与系统时钟同步运行。W982516行地址数目是13,列地址数目是9。与各种SDRAM一样,这种SDRAM具有以下几个特点:(1)采取行列地址复用原则,SDRAM的地址线在不同的命令下提供不同的地址,行列地址复用13根地址线。(2)需要定时刷新。(3)在进行读写时,需先激活行。换页读写时要预充关闭的行,然后再激活新的行进行读写。(4)SDRAM正常工作之前配置模式寄存器。SDRAM具有较多的控制命令,具体命令见表1。

表1 SDRAM命令

解析命令对应的Verilog代码如下:

always @(cmd)

begin

case(cmd)

modeset:begin nCS<=1‘b0; nRAS<=1‘b0; nCAS<=1‘b0; nWE<=1‘b0;end

refr: begin nCS<=1‘b0; nRAS<=1‘b0; nCAS<=1‘b0; nWE<=1‘b1;end

prech: begin nCS<=1‘b0; nRAS<=1‘b0; nCAS<=1‘b1; nWE<=1‘b0;end

actv: begin nCS<=1‘b0; nRAS<=1‘b0; nCAS<=1‘b1; nWE<=1‘b1;end

wrt : begin nCS<=1‘b0; nRAS<=1‘b1; nCAS<=1‘b0; nWE<=1‘b0;end

read: begin nCS<=1‘b0; nRAS<=1‘b1; nCAS<=1‘b0; nWE<=1‘b1;end

nop : begin nCS<=1‘b1; nRAS<=1‘b1; nCAS<=1‘b1; nWE<=1‘b1;end

endcase

end

3 SDRAM控制器的设计

3.1 系统设计框图

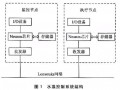

图1 系统设计框图

如图1,两片W982516并成32位数据总线的SDRAM。外部数据总线为32位,FIFO1为外部数据的一级缓冲,当FIFO1中的数据超过512时(SDRAM中一页的数据量),SDRAM控制器将数据从FIFO1中读出写入W982516暂存,当FIFO2中的数据剩余空间大于512时,SDRMA控制器从W982516读入一页数据写入FIFO2,硬盘控制器再将FIFO2中的数据写入硬盘。

3.2 SDRAM控制器设计

3.2.1 复位初始化

图2 SDRAM控制器设计框图

如图2,虚框内为初始化进程,SDRAM在上电后200us,由一个初始化操作来配置SDRAM的工作模式。在200us之内只能给SDRAM发NOP命令。初始化过程由启动以下指令流完成:首先由一个预充所有BANK指令完成对所有BANK的预充,然后是八个周期的自动刷新指令,最后在模式配置指令下完成SDRAM内部模式设置寄存器的配置。模式寄存器指定了突发长度、突发类型、CAS延时等详细的信息。为了方便灵活的应用,本设计中将SDRAM模式寄存器设置为0x027(突发长度为整页,CAS Latency为2)。只有成功的完成初始化过程,SDRAM才可以正常工作。

3.3.2 刷新计数模块

SDRAM要求在64ms之内对4096行进行刷新,也就是每15.6us刷新一行,由于系统时钟周期为13ns,所以刷新计数模块计数达到1170,就需要对SDRAM发出刷新命令。如图3,刷新计数模块计数到大于等于1170时,比较器输出上升沿到D触发器,D触发器输出高电平发出刷新请求,SDRAM控制器收到刷新请求后执行刷新命令。SDRAM控制器完成刷新命令后发出刷新应答信号将D触发器的输出端清零,同时将刷新计数器清零并重新计数。

图3 刷新模块

3.3.3 工作过程

FPGA完成对SDRAM芯片的初始化后,进入空闲状态,然后根据外部信号做出相应的动作,如自动刷新、读和写数据。如果收到自动刷新请求,则控制器向SDRAM发出自动刷新命令,自动刷新的优先级最高;如果FIFO1中的数据超过512个(如图1),则首先激活要写的行,然后再将数据写入SDRAM,最后经过预充电关闭这一行回到空闲状态,用一个寄存器记录SDRAM里有效数据的行数,此时有效数据的行数加1,行地址加1,写操作的优先级第二;如果FIFO2中的剩余空间超过512个并且有效数据的行数大于0时则可执行读操作,同写操作一样也需要首先激活要读的行,然后再将数据从SDRAM里读出写入到FIFO2,并经过预充电关闭这一行回到空闲状态,同时有效数据的行数减1, 行地址加1,读操作的优先级最低。这样就设计成一个64Mbytes的大容量循环缓冲。状态机在空闲时的状态转移代码如下:

work_idle:

begin

if(refresh)//收到刷新请求,优先级最高

work_state <= work_refresh;

else if(ff_halffull)//FIFO1缓冲半满,先写SDRAM

work_state <= work_write;

else if((wr_counter>0)&ff_halfempt) //FIFO2缓冲半空,读SDRAM

work_state <= work_read;

else

work_state <= work_idle;

end

4 总结

本设计已经成功运用于某型雷达,可记录大于40Mbytes/s的实时雷达信号。SDRAM控制器工作稳定,从而实现了低成本、大容量、高速度的设计目标。